최근 반도체 기업들에게 가장 큰 화두로 떠오르고 있는 단어는 단연 DTCO라고 할 수 있습니다. 공정 미세화가 물리적 한계에 다다르고 있기 때문에 이를 넘어설 돌파구로 DTCO가 급부상하고 있습니다.

반도체 파운드리 분야의 선두 기업인 TSMC와 삼성전자 두 기업 모두 반도체 미세공정 시대에 접어들면서 설계와 공정을 동시에 최적화하는 DTCO 전략에 집중하고 있으며, 그 방식과 강점은 일부 차이를 보입니다.

TSMC의 DTCO 전략

주요 특징

- 공식적으로 “What is DTCO?”라는 블로그에서, DTCO가 논리(Logic), SRAM, 아날로그, I/O까지 공정 기술의 전체 범위에서 설계-공정 간 상호작용을 최적화하는 것이라고 정의하고 있습니다.

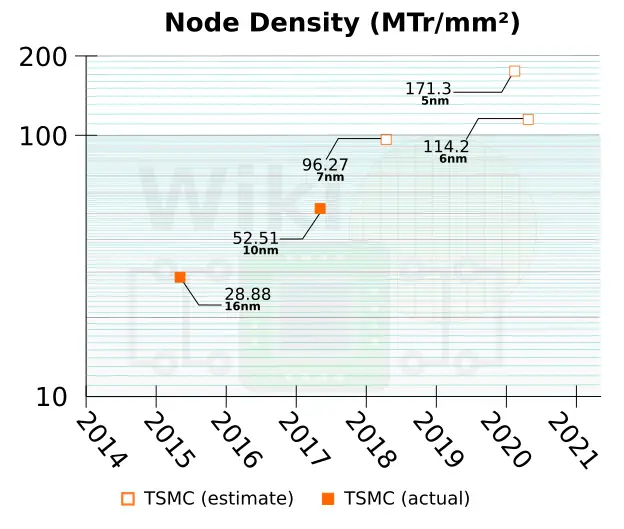

- 10 nm 대비 7 nm 노드에서 DTCO 덕분에 논리 밀도가 약 1.6배 증가, 속도가 약 20% 향상, 전력은 약 40% 절감했다고 발표했습니다.

- 고객사 설계-공정 협업을 “상호공생(symbiotic relationship)”으로 표현하며, 고객 설계팀과 공정팀이 초창기부터 긴밀히 협업하는 구조를 강조합니다.

- EDA/IP 생태계 구축에도 노력을 기울이고 있으며, “3DFabric Alliance” 등 반도체 설계-패키징-공정 에코시스템을 통해 DTCO 지원 체계를 갖추고 있습니다.

실제 설계 기술 협업 사례

- TSMC는 고객과 함께 칩 설계 초기에 설계 엔지니어와 공정 엔지니어가 함께 투입되어 설계 규칙(rule-set), 공정 가변성(process variability) 등을 설계 단계에서부터 고려하는 협업 모델을 갖고 있습니다.

- 교육/인재 양성 면에서도 TSMC는 ‘Advanced IC Design Program’을 운영하여, 설계 레이아웃 인력에게 DTCO 개념을 교육하고 협업 능력을 키우고 있습니다.

장점

- 노드가 깊어질수록 설계-공정 간 조율의 중요성이 커진다는 인식 아래, DTCO를 통해 PPA(Power-Performance-Area) 개선을 조직적으로 추진하고 있다는 점

- 고객 설계팀과의 조기 협업으로 공정 변화에 설계가 적응할 시간을 확보함으로써 위험(re‐spin) 없이 양산 가능성을 높이고 있다는 점

삼성전자의 DTCO 전략

주요 특징

- 자사 파운드리 부문에서 ‘GAA MBCFET™’ 구조를 적용한 DTCO 활동을 공식 블로그에서 소개하고 있습니다.

- 해당 글에서 “구조 변화(예: GAA) 이후에도 설계-공정 통합 최적화(DTCO)가 없으면 PPA 이점을 충분히 활용할 수 없다”고 명시하고 있습니다.

- DTCO의 예로 다음과 같은 설계-공정 관점 최적화를 언급합니다:

- 면적(Area) 감소를 위해 설계 배치(Layout)와 공정 배선(Wiring) 저항/정전용량(Capacitance) 등을 고려

- 성능(Performance) 향상을 위해 배선 저항 및 배치 거리 축소

- 전력(Power) 절감을 위해 낮은 동작전압과 우수한 트랜지스터 on/off 특성을 설계-공정에서 동시 고려

실제 설계 기술 협업 사례

- 3nm 노드에서 GAA MBCFET 구조가 적용될 때, 공정팀과 설계팀이 트랜지스터 구조(채널폭, 시트 형태), 배선 구조, 셀 라이브러리 등을 처음부터 재설계하여 PPA 이점을 최대화하는 활동을 수행했습니다.

- “최적의 조합 레시피를 구상하는 Chef”라는 표현으로 DTCO를 설명하면서, 설계팀과 공정팀이 함께 설계-공정 변수(trade-offs)를 탐색하는 과정이 강조되어 있습니다.

장점

- 트랜지스터 구조 혁신(예: GAA)과 함께 설계-공정 상호최적화(DTCO)를 병행함으로써 기존 미세화 경쟁 외에 설계-공정 통합 경쟁력을 갖추려는 흐름이 뚜렷합니다.

- 설계자 입장에서 설계 초기에 공정 제약을 반영할 수 있다는 점에서, 설계 리스크가 낮아질 수 있다는 장점이 있습니다.

두 기업 전략 비교 및 시사점

| 항목 | TSMC | 삼성전자 |

|---|---|---|

| DTCO 적용 범위 | 논리·SRAM·아날로그·I/O 전반, 설계-공정 협업 조기 시작 | 주로 논리 고성능 프로세스에서 GAA 구조 적용과 설계-공정 협업 중심 |

| 고객 설계 협업 방식 | 고객사 설계팀과 공정팀이 초반부터 공동 참여, 교육 프로그램 운영 | 내부적으로 설계-공정 팀 간 협업이 강조 |

| 생태계/EDA·IP 연계 | 3DFabric Alliance 등 생태계 구축을 통해 DTCO 지원 인프라 갖춤 | 설계-공정 최적화를 위해 구조 혁신과 DTCO 병행 강조, 패키징-시스템 측면 확대 중 |

| 전략적 강점 | 설계-공정 통합 최적화 경험이 더 풍부하며, 다양한 고객사와 설계 협업을 통한 노하우 축적 | 트랜지스터 구조에서 혁신(예: GAA MBCFET™)을 이끌며, 설계-공정 통합으로 PPA 향상을 목표 |

| 전략적 리스크 | 고객사 요구와 설계 다양성에 따른 복잡성 증가, 디자인 자산 대응 필요 | 노드 전환 과정 및 수율/양산 차별화 이슈 존재, 설계-공정 최적화 경험이 상대적으로 짧을 수 있음 |

시사점

- 두 기업 모두 DTCO를 통해 단순한 공정 미세화뿐 아니라 설계와 공정이 함께 진화해야 한다는 인식을 공유하고 있습니다. 실제로 삼성 측도 “공정 미세화만으로는 10-15% 개선에 불과하다”라고 하고 있습니다.

- 설계자 관점에서 보면, 공정 제약을 설계 초기 단계에서 반영할 수 있다는 점에서 DTCO는 설계 리스크를 줄이고 시장 출시(TTM: Time-to-Market)를 단축할 수 있습니다.

- 설계-공정 간 협업 모델이 복잡하다 보니, 기업별로 경험률과 생태계 지원 수준에서 차이가 나며, 특히 고객 설계사와의 협업 경험이 풍부한 TSMC가 유리한 측면이 눈에 띄고 있습니다.

- 고성능 컴퓨팅(HPC), AI, 자율주행 등 차세대 응용처에서는 PPA 최적화가 더욱 중요해질 것으로 보이며, DTCO 전략은 경쟁력의 중심점 역할을 할 가능성이 높습니다.

TSMC와 삼성전자는 모두 DTCO를 반도체 설계·공정 혁신의 핵심 전략으로 삼고 있으며, 설계-기술 협업 모델을 통해 PPA 개선 및 시장 대응력을 확보하려 하고 있습니다. TSMC는 설계-공정 통합을 오랜 기간 추진해온 경험과 생태계 연계 측면에서 강점을 보이며, 삼성전자는 트랜지스터 구조 혁신과 설계-공정의 병행 최적화로 차별화를 시도하고 있습니다.